To learn and find out more, please click on the link and register your interest https://link.growthflow.ai/widget/form/FDFJBysxtKRdh8Y1jWng?notrack=true

Exception Model in ARM Cortex-Mx Processor: A Deep Dive into STM32F411RE Microcontroller

The ARM Cortex-Mx processor used in the STM32F411RE microcontroller features an efficient and sophisticated exception model. This model handles system interrupts, faults, and other exceptions, ensuring the stability and real-time performance of the microcontroller. To leverage the full potential of Cortex-Mx processors in embedded systems, understanding the exception model is crucial.

In this SEO-optimized blog post, we will explore the exception model, its key components, and how it is implemented in the STM32F411RE microcontroller.

Table of Contents:

- What is the Exception Model in ARM Cortex-Mx Processors?

- Types of Exceptions in STM32F411RE

- Exception Priorities in ARM Cortex-M4

- Vector Table and Exception Handling Process

- Understanding Fault Exceptions

- Configuring Exceptions in STM32F411RE

- Summary

1. What is the Exception Model in ARM Cortex-Mx Processors?

In the ARM Cortex-Mx architecture, the exception model provides a standardized way to handle external interrupts, system faults, and software-generated events. Exceptions in this model include both interrupts (triggered by external events like timers or GPIO pins) and faults (triggered by system errors or invalid operations).

The Cortex-M4 processor, which powers the STM32F411RE microcontroller, supports a low-latency exception handling mechanism. This feature ensures rapid response to interrupts while maintaining low power consumption, making it ideal for real-time embedded systems.

The exception model includes:

- A vector table that holds the addresses of exception handlers.

- Prioritization of exceptions to determine which one should be serviced first.

- Stacking and unstacking mechanisms to preserve the processor’s state during exception handling.

2. Types of Exceptions in STM32F411RE

The STM32F411RE microcontroller supports three main types of exceptions:

1. System Exceptions

System exceptions are internal to the processor and manage critical system operations. These include:

- Reset: Triggered when the microcontroller is reset.

- NMI (Non-Maskable Interrupt): A high-priority, non-maskable interrupt that cannot be disabled by software.

- HardFault: Triggered by system errors such as invalid memory access.

- SVCall (Supervisor Call): A software-triggered interrupt used by the operating system for context switching or privileged operations.

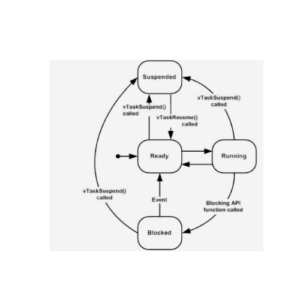

- PendSV: Used in context switching in RTOS systems to manage task scheduling.

2. External Interrupts

External interrupts are triggered by peripherals, timers, or external devices connected to the microcontroller. The STM32F411RE supports multiple external interrupts via the EXTI (External Interrupt/Event Controller). Examples include:

- Timer interrupts.

- GPIO interrupts.

- Communication peripherals such as UART, SPI, and I2C.

3. Fault Exceptions

Fault exceptions are triggered by unexpected system behaviors or errors. These include:

- MemManage Fault: Occurs when a memory protection violation is detected.

- BusFault: Triggered by an error during a memory access operation.

- UsageFault: Triggered by errors such as divide-by-zero or illegal instruction execution.

3. Exception Priorities in ARM Cortex-M4

In the ARM Cortex-M4 processor, each exception is assigned a priority level. Higher priority exceptions will preempt lower priority ones, ensuring that critical system tasks are serviced promptly.

Priority Numbering

- Lower numbers indicate higher priority. For example, an exception with priority level 0 is serviced before an exception with priority 1.

- Cortex-M4 processors support up to 256 levels of priority, although STM32F411RE typically uses a 4-bit priority field, offering 16 priority levels (0–15).

Preemption

Exceptions with higher priority can preempt those of lower priority. For example, if a GPIO interrupt occurs while a SysTick interrupt is being handled, the GPIO interrupt (with a higher priority) will be serviced first.

4. Vector Table and Exception Handling Process

The vector table is a crucial part of the exception model in ARM Cortex-Mx processors. It is a memory structure that holds the addresses of exception handlers.

Location of Vector Table in STM32F411RE

- In the STM32F411RE, the vector table is located at the base address of the memory, 0x0800 0000 (flash memory).

- The table starts with the initial value of the stack pointer, followed by the addresses of various exception handlers.

Exception Handling Process

When an exception occurs:

- The processor saves the current context (registers and processor state) onto the stack.

- The processor retrieves the address of the appropriate handler from the vector table.

- The exception handler is executed.

- After handling the exception, the processor restores the previous context and resumes normal execution.

5. Understanding Fault Exceptions

Fault exceptions are triggered when the processor detects an error. These exceptions help identify issues such as memory access violations, bus errors, or invalid operations.

1. HardFault

- HardFault is the most severe fault exception and occurs when other fault handlers (like MemManage, BusFault, or UsageFault) are disabled or if they escalate to an unrecoverable error.

- It can be triggered by invalid memory access or divide-by-zero errors.

2. MemManage Fault

- Triggered when there’s a violation of memory protection rules, such as accessing restricted memory regions.

- Can be used to implement memory protection schemes.

3. BusFault

- Occurs during faulty memory accesses due to issues like unaligned access or accessing non-existent memory regions.

4. UsageFault

- Triggered by invalid operations such as undefined instructions, divide-by-zero, or unaligned memory access.

Example: Handling a HardFault Exception

Here’s a basic template for handling HardFault in STM32F411RE:

void HardFault_Handler(void) { // Add code to log the error and reset the system while (1); }

6. Configuring Exceptions in STM32F411RE

To configure exception handling in STM32F411RE, follow these steps:

1. Enable the Interrupt in the NVIC

The NVIC (Nested Vectored Interrupt Controller) manages exception priorities and enables/disables specific interrupts. Use the following code to enable a specific interrupt:

NVIC_EnableIRQ(TIM2_IRQn); // Enable Timer 2 interrupt

2. Set Exception Priorities

Use the NVIC_SetPriority() function to set the priority of an exception:

NVIC_SetPriority(TIM2_IRQn, 2); // Set Timer 2 interrupt priority to 2

3. Write the Interrupt Service Routine (ISR)

Every exception has a corresponding ISR that handles the exception. Here’s an example of a basic ISR for Timer 2 interrupt:

void TIM2_IRQHandler(void) { // Clear interrupt flag TIM2->SR &= ~TIM_SR_UIF; // Handle Timer interrupt }

7. Summary

The exception model in the ARM Cortex-M4 processor of the STM32F411RE microcontroller plays a critical role in handling interrupts and faults efficiently. By understanding the different types of exceptions, their priorities, and how to configure them, you can optimize your embedded system for real-time performance.

From system exceptions like HardFaults to external interrupts triggered by peripherals, mastering the exception model is essential for building reliable and responsive embedded applications on the STM32F411RE.

Ensure that your exception handlers are efficient and appropriately prioritized to prevent system crashes and ensure timely responses to critical events. With the right configuration, the STM32F411RE can handle complex applications that require real-time multitasking and fault tolerance.

By mastering the exception model in ARM Cortex-Mx processors and STM32F411RE, you can build resilient, high-performance embedded systems that stand up to real-world demands.

To learn and find out more, please click on the link and register your interest https://link.growthflow.ai/widget/form/FDFJBysxtKRdh8Y1jWng?notrack=true